Dec. 12, 1961

## F. C. WILLIAMS ET AL

ELECTRONIC DIGITAL COMPUTING DEVICES

Original Filed June 1, 1950

Original Filed June 1, 1950

Original Filed June 1, 1950

FIG.3.

F16.5.

Original Filed June 1, 1950

Original Filed June 1, 1950

Original Filed June 1, 1950

Original Filed June 1, 1950

Original Filed June 1, 1950

Original Filed June 1, 1950

FIG.11.

Dec. 12, 1961

### F. C. WILLIAMS ET AL

3,012,724

ELECTRONIC DIGITAL COMPUTING DEVICES

Original Filed June 1, 1950

3,012,724

ELECTRONIC DIGITAL COMPUTING DEVICES

Original Filed June 1, 1950

Original Filed June 1, 1950

Original Filed June 1, 1950

Original Filed June 1, 1950

Original Filed June 1, 1950

Original Filed June 1, 1950

Original Filed June 1, 1950

Fig. 22.

# United States Patent Office

1

3,012,724

ELECTRONIC DIGITAL COMPUTING DEVICES

Frederic Calland Williams, Romiley, Tom Kilburn,

Davyhulme, Manchester, Maxwell Herman Alexander

Newman, Altrincham, and Geoffrey Colin Tootill,

Hawley, Camberley, England, assignors, by mesne assignments, to International Business Machines Corporation, New York, N.Y., a corporation of New York

Original application June 1, 1950, Ser. No. 165,434, now

Patent No. 2,810,516, dated Oct. 22, 1957. Divided

and this application July 22, 1957, Ser. No. 673,522

Claims priority, application Great Britain June 22, 1949

48 Claims. (Cl. 235—157)

This invention relates to electronic digital computing machines and is particularly, although by no means exclusively, concerned with binary-digital computing systems which employ digital storage or memory devices of the type described in the paper by F. C. Williams and T. Kilburn, Proc. Institution of Electrical Engineers, part III, March 1949, pages 81-100.

This application is a divisional application from application Serial No. 165,434, filed June 1, 1950, by F. C. Williams et al., for "Electronic Digital Computing Devices."

Universal digital computing machines, i.e. computing machines which are intrinsically capable of performing any computation desired, provided that adequate storage is provided, operate by handling a mathematical problem as a series of simple arithmetic operations which can be performed upon numbers which are held in a storage or "memory" within the machine. Such machines, in general, conform to a similar pattern. In these machines there exists a store in which all data required in the solution of a problem is recorded, each element of data having a unique location or "address" defined by its spatial or temporal position or by a combination of both, one or more arithmetic organs, which generally include a subsidiary store or accumulator, in which elementary arithmetical operations can be performed between numbers fed (generally at different times) to the arithmetic organ, and finally a control system which controls the sequence of operations of the machine and orders the necessary transfers of numbers and arithmetical operations.

For any particular problem the programme of operations to be carried out by the machine is broken down into a series of orders, each of which represents an elementary number transfer or arithmetical operation. These orders may be conveniently expressed in code form as numbers and stored in the memory of the computing 50 machine, as part of the data of the problem, until required and called into operation by the control system of the machine. Each step of operation performed by the machine in response to a single order may be reduced in effect to the transfer of a number between the store 55 and some other portion of the machine (in general the arithmetic organ) and an arithmetical operation may or may not occur automatically as a result of the transfer. For example, two numbers may be added by first feeding one number from the store to the arithmetic organ, where it is stored in an accumulator, as a result of a first order or instruction and then feeding the second number from the store to the arithmetic organ, under the control of a second instruction, in such a fashion that it is added to 65 the first number held in the accumulator. The coded order or instruction "words" therefore have to define the addresses in the main store of the machine from which or to which a number transfer is to occur and must also define the other destination or source of the transferred 70 number and any arithmetical operation which is to occur as a result of the transference.

2

The obeying of each single instruction by the machine may be regarded as the fundamental unit of operation of the machine and the interval involved in the obeying of an instruction is referred to hereinafter as a "bar." A sub-interval or, as it is sometimes referred to, a minor cycle is occupied by the time taken to express within the machine in dynamic form a number or instruction word. Such intervals are referred to as "beats." It is apparent that any number transference must by itself occupy one beat as, in order to transfer a number or word which exists in static form in the store to another address where it is again represented in static form, it is necessary to convert the number or word to dynamic form and that such conversion is the essence of the transfer as any digit of a number or word existing transiently in dynamic form may be employed to recreate its static counterpart immediately in a storage location.

In working through a problem the computing machine normally obeys instructions sequentially and as the instruction words are stored in the main storage system of the machine each instruction word has to be read out in turn in dynamic form, the process of reading involving the transient identification of each digit of a word held in a store and the simultaneous provision of a transient signal representative of the digit, so that the word may effect the necessary control functions in the machine which are requisite for the obeying of the instruction. The sequential selection of instruction words from the store must be performed by a subsidiary controlling function of the machine; the utilization of each instruction word in the store necessarily involves in effect a transfer of that word out of the store and may be effected under the direction of a "control instruction" which is held in a subsidiary storage portion of the machine. It is arranged that upon the completion of the operation of obeying each instruction, the control instruction relating to the next instruction in the sequence to be obeyed is caused to become effective and initiate the events occupying the next bar in the operation of the machine. The control instructions required when instructions recorded in specified addresses in the store are to be selected sequentially may be readily derived, for example, by the operation of a completion signal at the end of each bar.

The automatic process of sequential selection of instructions may require to be broken automatically in certain circumstances. For example, transfer of the control exercised by the control instructions may be required to take place in response to an arbitrary instruction in the sequence, possibly a reversion to an instruction previously used or a jump ahead to a new instruction. Such transfers of control may occur as the result of a test made upon the state of a partial solution existing in the computing machine and the conditional transfer may be produced by appropriate arrangement of the instructions recorded in the store when the programme for the problem on hand was designed. For example, a particular group of q instructions whose addresses may be denoted as n+1, n+2 ldots n+q-1, n+q may be repeated if, at a particular stage in the solution of a problem the partial solution available complies with a certain requirement (e.g. of sign), while if the requirement is not complied with the machine may be required to progress to a new set of instructions. Such a conditional transfer of the control of the machine may be effected by arranging that instruction n+q-1 calls for the necessary test of the partial solution and that when instruction n+q-1 has been obeyed, causing the machine to proceed either to instruction n+q, or by omitting one instruction, to instruction n+q+1 in dependence upon the result of the test. Instruction n+q may be designed to cause a backward transfer of control by causing the machine to subtract a quantity q from the

4

control instruction number, the number q being obtained from the store wherein it was originally loaded as part of the data, so that the control instruction reverts to instruction n. The instruction n+q+1 on the other hand may be designed to allow the solution to proceed. Other arrangements may be made for control transfer; for example, an instruction n, selected by the control instruction after an instruction calling for a test has been completed, may require control to be transferred to an entirely new instruction in address location m and this 10 may be achieved by causing the instruction n to replace the control instruction by a number m-1 so that the normal sequential selection function performed by the control instruction mechanism causes the instruction m to be next selected. Alternatively, the instruction n may 15 be designed to cause the number (m-1)-n to be added to the existing control instruction number with the same effect.

One existing form of computing machine of the general type outlined above comprises a memory, referred to 20 as the Main Store, which consists of a number of cathode ray tube storage units operating upon the principles described in the aforesaid paper by F. C. Williams and T. Kilburn. The machine operates in the serial mode, cally as trains of pulses in common channels and each word occupies an "address" comprising a line or portion of a line on one cathode ray tube of a raster-like pattern applied in common to all the cathode ray tubes in the observation and reproduction in dynamic form of that word during one beat without destruction of the recorded word may be achieved by scanning of the appropriate address line in the appropriate cathode ray tube of the Williams and T. Kilburn, the cathode ray tube store systems require for their operation that all the recorded information should be periodically regenerated, and this may be most conveniently carried out by arranging that so called "scan," beats according to a cyclic pattern while during intervening, or so called "action," beats selected addresses are made "active," i.e. the contents of a single selected address are made available for reading.

interlaced scan and action beats, when taken in conjunction with the provision of a main store in which both data and instruction words are initially recorded, results in a rhythm of operation for the machine in which each bar normally comprises four beats. The above-mentioned existing machine, in order to operate in this rhythm, comprises in addition to the main store referred to above and an arithmetic organ, two subsidiary stores which perform the controlling function for the machine. These stores, each of which is of the cathode ray tube type, each has a capacity of one word and the first, which was known as the "control register," recorded a number which is referred to in this specification as the "control instruction" and which is effectively a number defining the address in the main store of an instruction which is 60 being currently obeyed, while the second store, which was known as the "current instruction store," acts as an intermediate repository for each "current instruction word" read from the Main Store before that instruction word is fed to perform its address selection and controlling func- 65 tions. In simple operation during the first (Scan 1) beat of a bar the control instruction number (n) is caused to be increased by one, by means of a suitable adding circuit associated with the regenerative loop of the control register store, and the number n+1, which is simultaneously read out, performs the selection of the address in the main store of the next instruction to be obeyed. During the next (Action 1) beat the selected instruction word is read out of the Main Store and written into the

(Scan 2) beat when it is read out of this subsidiary store and fed to the address selection and routing control mechanism to prepare the source and destination and direction of transfer which will be involved in the word transfer comprised in the obeying of this instruction in the next beat. During the fourth (Action 2) beat this instruction will be obeyed, a number or instruction word being transferred between an address in the Main Store and some other part of the machine (generally the arithmetic organ when a number is being transferred, but possibly the control register if a control transfer is being effected) and will generally be completed in the single beat. If, however, the instruction is one which calls for an arithmetic operation occupying more than one beat then provision is made for holding up the initiation of the next bar until the scan beat following the beat in which the completion of instruction occurs. In the aforesaid existing machine it was assumed that the instruction words represented in a coded form the address in the Main Store and the address in the arithmetic organ (or elsewhere) between which a number transfer was to be effected and that one digit of the instruction word defined the direction in which the transfer was to occur.

The object of the present invention is to provide an i.e. numbers in binary notation are represented dynami- 25 improved computing machine similar in general principle to such existing machine previously referred to in which economy of apparatus, increased facilities of operation and enhanced operating speed may be achieved.

According to one feature of the invention the machine store. Reading of a particular word in the store, i.e. the 30 comprises a main storage device for recording both number and instruction data to be employed in the solution of a problem, an arithmetical organ for performing a chosen operation upon or between numbers or words fed thereto from said main storage device and a control sysstore. As explained in the aforesaid paper by F. C. 35 tem including means for storing and utilising a control instruction word and means for storing and utilising a particular or present instruction word selected and transferred from said main storage device under the control of said control instruction word characterized in that the sequential regeneration takes place during alternate, or 40 storage of both said control instruction word and said present instruction word are effected within a single storage unit.

According to another feature of the invention the selection of the desired data from the main storage device The mode of operation of the storage system with such 45 and the controlling of the subsequent operation to be performed therewith within the machine are effected through the intermediary of different digit portions of a common instruction word.

> According to a further feature of the invention the 50 machine is provided with means for testing a partial solution and, in accordance with the result of such test, effecting conditional transfer of the control of instruction word selection to one or more different instruction words.

As already explained, machines of the general form de-55 scribed normally operate in a rhythm of four beats to a bar but in accordance with yet a further feature of the invention a second storage device is provided for recording instruction words and the operation of the machine then arranged to take place in a bar consisting of two beats only during the first of which a chosen instruction word is read out from said second storage device and is used to prepare means for selecting a data item from the first or main storage device and to prepare means for performing the required arithmetical or other operation while during the second beat such operations upon said data are obeyed whilst the control means simultaneously select the next instruction word in the second storage device in readiness for the next following operation. Such feature of the invention is particularly adapted for use with storage devices which require repeated regeneration of the data held therein in which case the respective regeneration or scan beats and the operative or action beats of the first and second storage devices are interleaved so current instruction store where it is held until the next 75 that the instruction storage device performs an action

beat while the main storage device performs a scan beat and vice versa.

In many applications the maximum number of digits required for the composition of the coded instruction word is less than half the number of digits which are required to provide the chosen maximum number capacity of the machine. The storage of these smaller words in positions within a storage device capable of accommodating the required maximum size of number or word is obviously wasteful and in accordance with yet another feature of 10 the invention a computing machine employing digital storage or memory devices, such as cathode ray tube devices, for recording separate items of numerical or coded instruction data of predetermined maximum magnitude at locations which each have a unique address within the 15 device is provided with arrangements for recording a plurality of items of appropriately smaller maximum magnitude within one unique address location of said device. Conveniently selection of any desired one of such plurality of items is performed upon a time-division basis.

The design and size of a given machine is governed largely by the maximum number of digits required in any number to give the desired degree of precision. While economic factors may restrict the maximum chosen to a value capable of properly handling only the majority of 25 problems which may require to be solved, there are not infrequently occasions, such as when many arithmetical operations are performed in succession upon the input numbers or if the latter are raised to high powers, when it may be necessary to use in the expression of any one 30 number, a greater number of digits than the chosen maximum of the machine, and in accordance with yet a further feature of the invention, the facility for doing this is provided in a machine operating in the serial mode and including an arithmetical organ which comprises a stor- 35 lated to the arrangement of FIG. 17, while age device of the cathode ray tube type wherein the maximum number of digits of a basic number or word are normally accommodated within one line scan on the screen of said tube by arranging the arithmetical organ to have a storage capacity of two lines, each line being 40 capable of storing one basic word or number.

With a view to increasing the flexibility of the machine it is frequently arranged that stored instruction words can themselves be modified from time to time in order to carry out an extended range of different functions. This  $_{45}$ is customarily effected by treating the instruction word as a number and passing it through the arithmetical organ where the desired alteration is made by the simultaneous feeding to such organ of a modifying word. Such a process involves waste of normal operating time of the ma- 50 chine and in accordance with yet a further feature of the invention a subsidiary storage device capable of storing one or more words is provided and the machine is arranged so that, in its normal operation, as each instruction word is read out of its normal storage location and 55 is fed to the control system of the machine, it is passed through a modifying device whereby it may, if desired, be modified by the simultaneous application to such device of a word from said subsidiary storage device.

In order that the various features of this invention may 60 be readily understood a detailed description of one complete universal digital computing machine together with detailed descriptions of a number of further modifications will now be given in conjunction with the accompanying drawings in which:

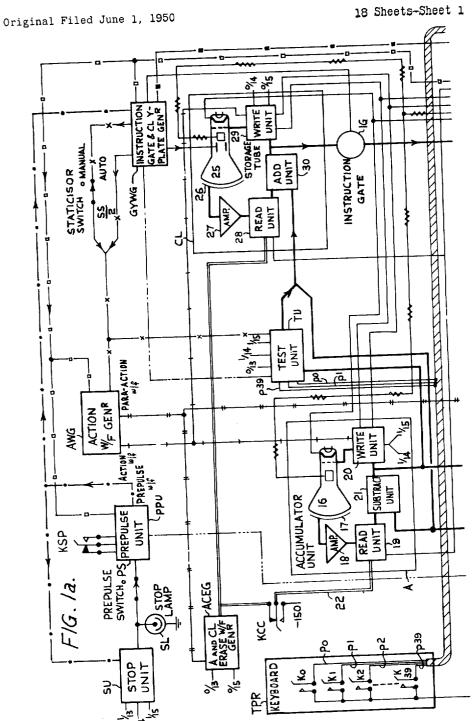

FIGS. 1a and 1b form, in combination, a block schematic diagram of a complete digital computing machine in accordance with certain features of the present invention.

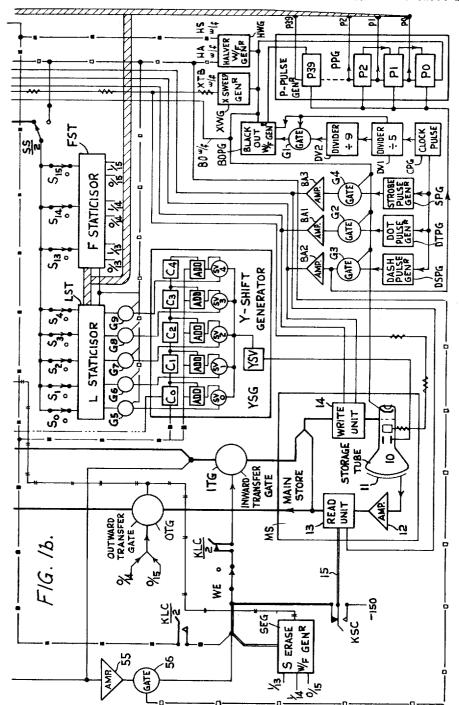

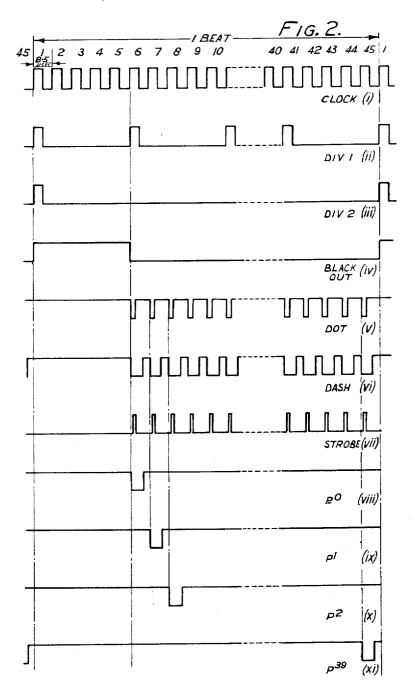

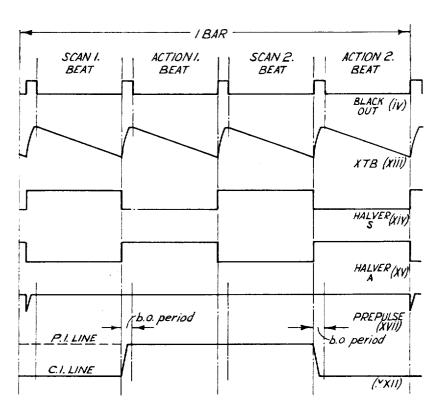

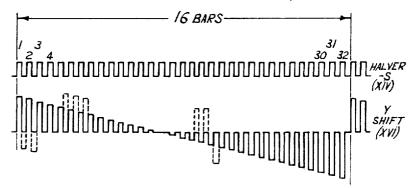

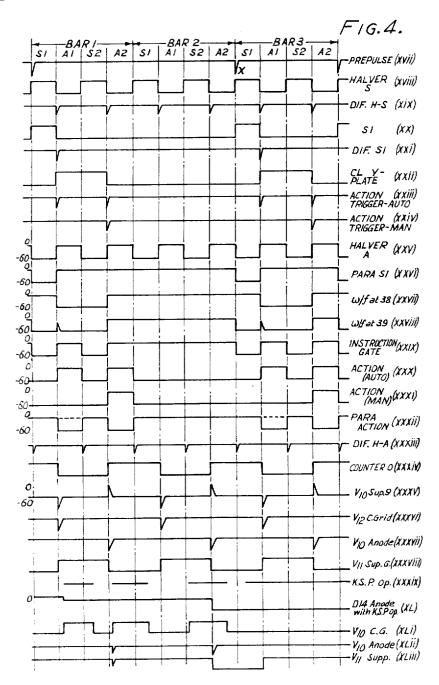

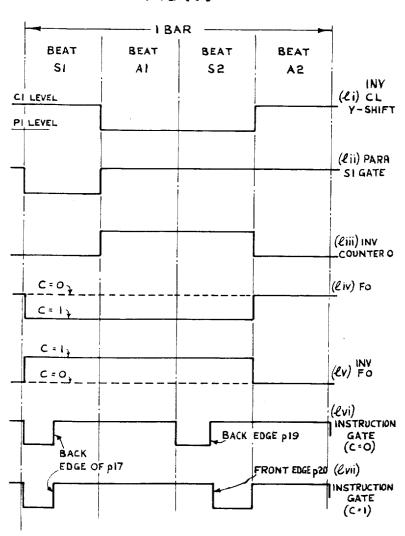

FIGS. 2, 3, 4 and 5 illustrate a series of waveform 70 diagrams relating to various parts of the machine shown in FIGS. 1a and 1b.

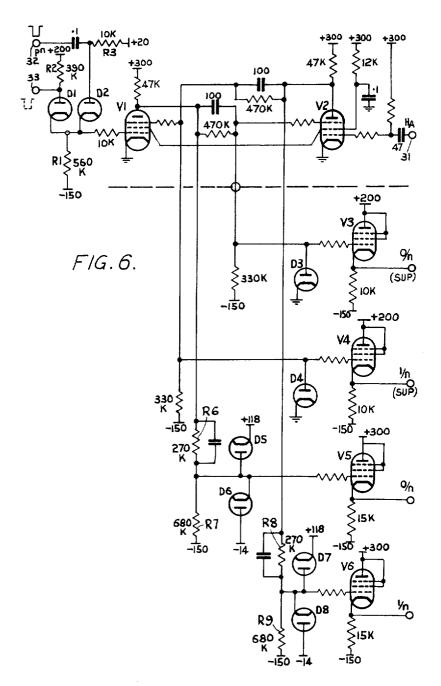

FIG. 6 is a detailed circuit diagram of one section out of several similar sections of the L and F Staticisor units of FIG. 1b.

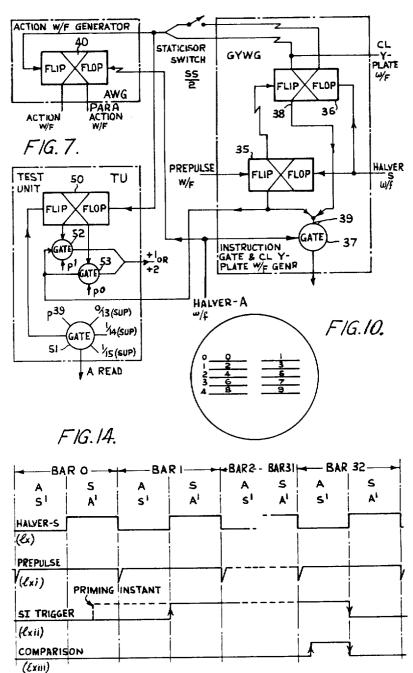

FIG. 7 is a more detailed block schematic diagram of the Instruction Gate and Y-Plate waveform generator for the control unit of FIG. 1a.

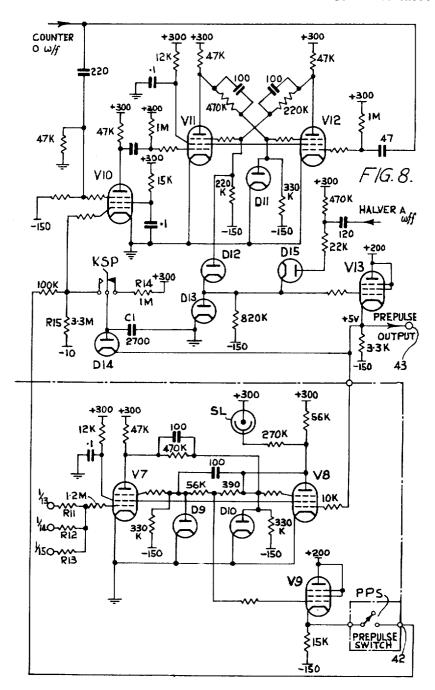

FIG. 8 is a detailed circuit diagram of the stop and prepulse units of FIG. 1a.

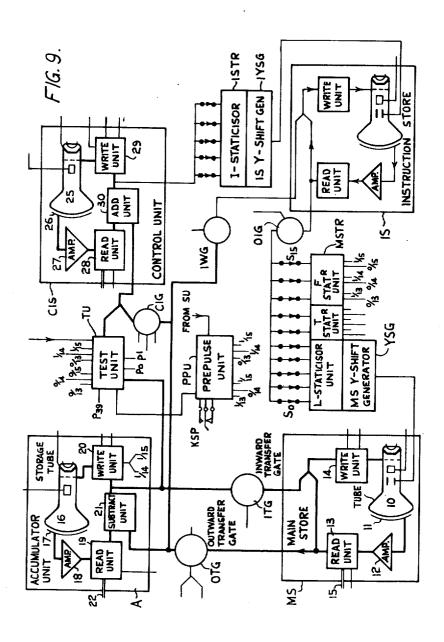

FIG. 9 is a block schematic diagram similar to FIG. 1 but of somewhat simplified character illustrating a modified machine arrangement.

FIG. 10 is a diagrammatic view of a storage tube screen showing the storage arrangements for shortened instruction words according to a further modification of the invention.

FIG. 11 is a series of waveform diagrams relating to the modification shown in FIG. 10.

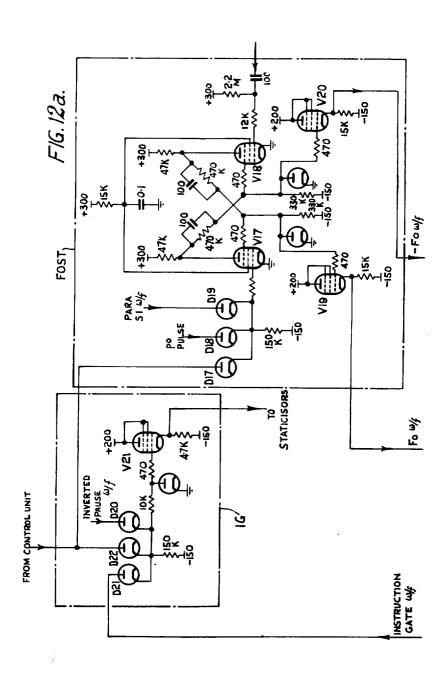

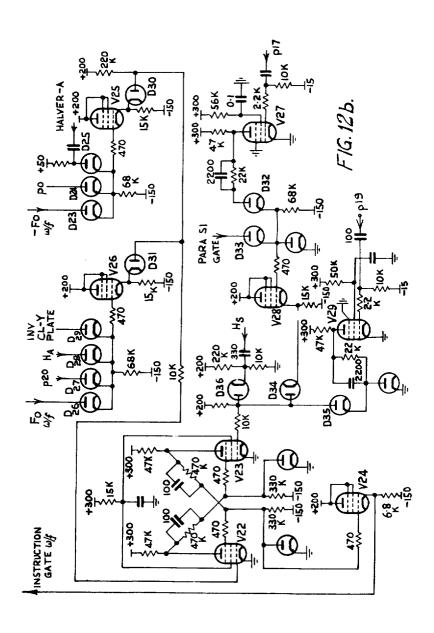

FIGS. 12a and 12b show a detailed circuit arrangement for the special F staticisor unit required in a machine similar to that of FIG. 1 but modified in accordance with the further embodiment illustrated in FIGS. 10 and 11.

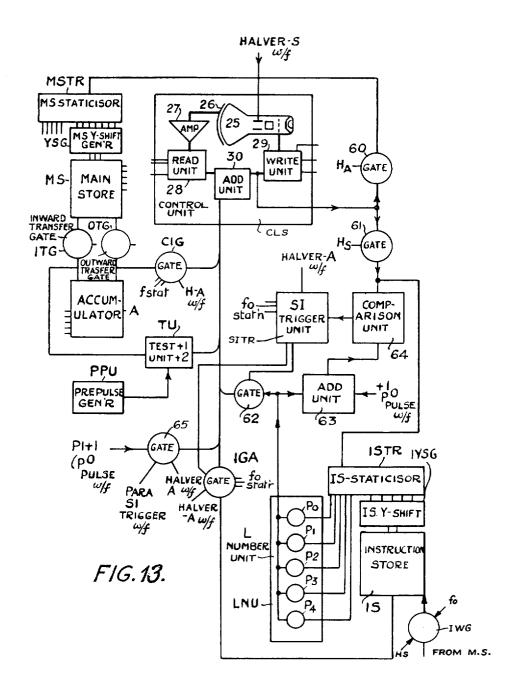

FIG. 13 is a block schematic diagram, again generally similar to FIG. 1 but illustrating yet a further modification of the invention.

FIG. 14 shows a number of waveform diagrams illustrating the modification of FIG. 13.

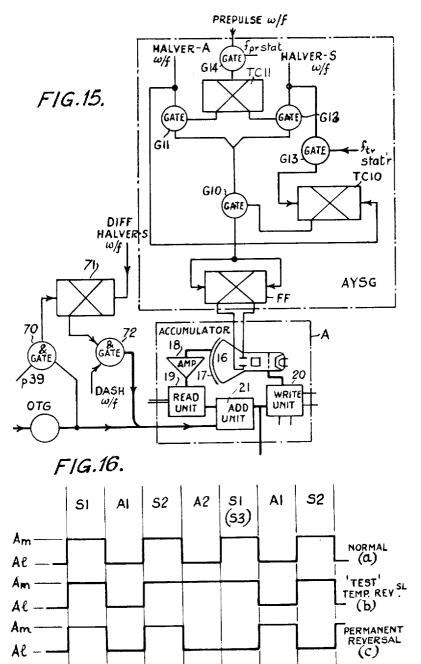

FIG. 15 is a block schematic diagram of a portion of the machine shown in FIG. 1 and relating to yet a further modification of the invention.

FIG. 16 shows a number of waveform diagrams related to the arrangement of FIG. 15.

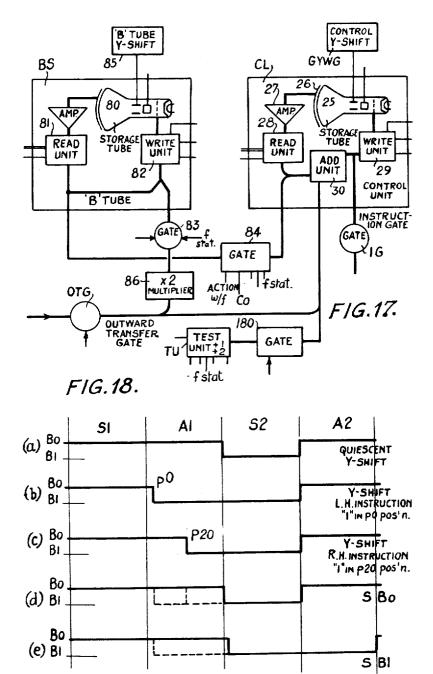

FIG. 17 is a further schematic block diagram of fragmentary character showing certain further modifications of the arrangement shown in FIG. 1 to explain another modification of the invention.

FIG. 18 comprises a series of waveform diagrams re-

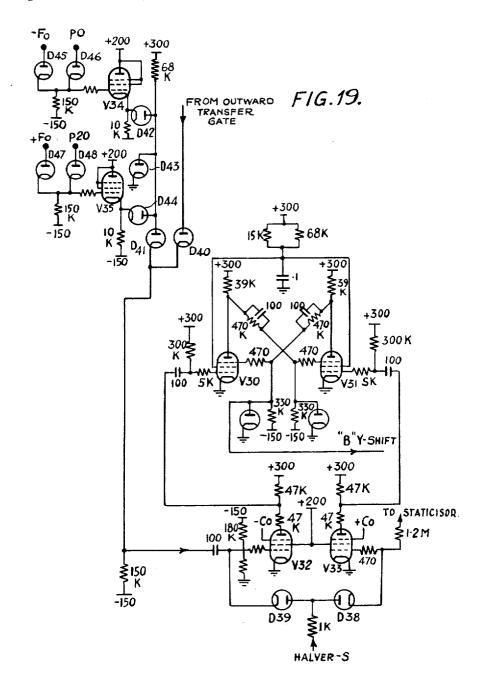

FIG. 19 is a detailed circuit arrangement for generating the particular form of Y-shift waveform disclosed in FIG. 18.

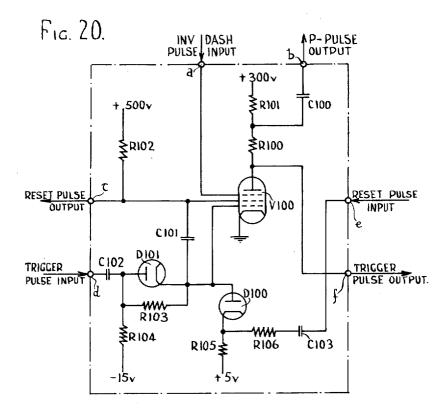

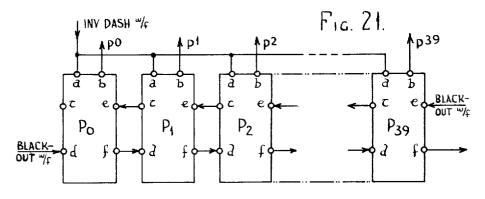

FIG. 20 is a detailed circuit diagram of one element of the pulse generating circuit PPG, FIG. 1b while FIG. 21 is an amplified block schematic diagram showing the interconnection of a plurality of such elements to form the complete device.

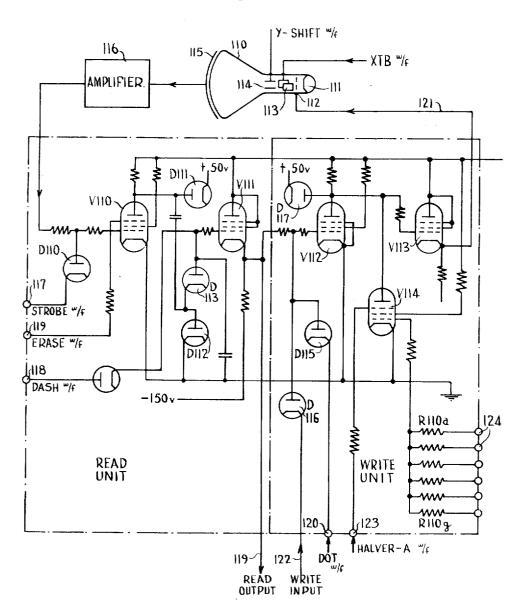

FIG. 22 is a part schematic, part detailed circuit diagram of a cathode ray tube storage device as employed in the Main Store MS, the accumulator, the control unit CL and other elements of the machine.

The general arrangement and method of operation of the particular embodiment chosen for illustration of the invention will first be described in broad outline with reference to the schematic diagram of FIGS. 1a and 1b. This machine operates under the binary system and is of the serial type. It utilises for various "memory" storage purposes cathode ray tube storage means of the kind described in the aforesaid paper by F. C. Williams and T. Kilburn, wherein each binary digit "0" or "1" of a number or the equivalent coded address or instruction word is represented by one or other of two, e.g. "dot" or "dash" forms of discrete electric potential charge upon the screen of a cathode ray tube. The group of sequential dot and dash charges comprised in each number or word are arranged along the whole or part of a single linear deflection scan of the cathode ray tube beam so that, when required, a plurality of such numbers or words may be recorded and stored side by side, by causing the beam to provide a television type raster. Selection of any desired number or word can then be achieved by arranging for the appropriate positioning of the tube beam in the transverse or "Y" direction before commencing its linear or "X" scanning movement.

The machine shown in FIGS. 1a and 1b comprises a Main Store MS (FIG. 1b) which includes one or more cathode ray tube storage devices as referred to above arranged for side-by-side or raster type line storage and pro-75 vided with the necessary ancillary apparatus by which numbers or words, in the form of pulse trains, can be written thereinto, read out therefrom, erased or continuously regenerated. Associated with this Main Store MS is a Y-Shift generator unit YSG for providing the requisite transverse or Y-deflection to the beam of the cathode ray tube of the Main Store for selecting any chosen one of the raster lines. The operation of this unit YSG is itself controlled during certain portions of the operation cycles of the machine by an L-Staticisor unit LST (FIG. 1b) whose function is to translate a dynamic pulse form signal into suitable static control voltages for the unit YSG whereby the latter provides a deflection of the tube beam in the Main Store MS to a raster line whose address is that indicated by the pulse signal fed to the staticisor unit.

The machine shown is capable of performing one simple type of arithmetical operation only, namely subtraction and this is effected in the arithmetical organ or Accumulator A (FIG. 1a) which includes a single cathode ray tube storage device arranged to deal with only one number or word at a time and provided with the requisite writing, reading, erasing and regenerating ancillary apparatus

The control of the various elements of the machine during each bar in obedience to the particular instruction of the moment is effected by the control unit CL (FIG. 25 1a), which includes a single cathode ray tube storage device arranged for two-line storage and provided with the requisite ancillary apparatus for effecting writing in, reading out, erasing and regenerating each of the two stored words. This ancillary apparatus also includes means by which an externally applied number, in the form of a pulse signal, may be added to a word already in the store.

The necessary transverse or Y-deflection of the beam of the cathode ray tube in the control unit CL in order to deal with the appropriate one of the two stored words, is controlled by an Instruction Gate and Y-Plate waveform generator unit GYWG (FIG. 1a) which is itself controlled in its operation by certain fundamental timing waveforms existing within the machine.

The machine being described operates at a rhythm of 40 four beats to each bar and the initiation of each bar is controlled by a special pulse waveform, hereinafter called a "prepulse" generated within a Prepulse Unit PPU. This unit is provided with a manually operable key KSP which serves, when thrown, to cause the release of a single prepulse only.

For the purpose of automatically changing the instruction word at the end of each bar so that the various sequential operations as defined by the programme laid down for the machine are effected in order the Test Unit 50 TU (FIG. 1a) is provided and serves, in combination with the ancillary adding apparatus of the control unit CL, normally, to add 1 to the address number of a word stored in the latter. This test unit TU also comprises means for determining the compliance or otherwise of a solution 55 number existing within the Accumulator A with a certain requirement, e.g. of its sign, and dependent upon the result of such test, for altering the aforesaid addition of 1 to an addition of 2.

For the purpose of stopping the automatic cyclic operation of the machine under certain circumstances there is provided a Stop Unit SU (FIG. 1a) with which is associated a warning or Stop Lamp SL.

A typewriter TPR (FIG. 1c) provided with a plurality of keys each significant of a different one of the total number of digit positions available in each number or instruction word is provided for initial setting up and testing purposes.

The routing of the various signals between units of the machine and the choice of its manner of operation are controlled through the intermediary of a number of gate or equivalent circuits among which are the Inward Transfer Gate ITG (FIG. 1b), the Outward Transfer Gate OTG (FIG. 1b) and the Instruction Gate IG (FIG. 1a).

These gates and other circuits are controlled by the static 75 section of the word. In general with a machine of the simplest type described a total of five binary digit symbols will suffice to select any desired address level while a total of three binary digit symbols is sufficient to set up any of the different function operations which can be carried out. Accordingly the 1st, 2nd, 3rd, 4th and 5th digits of the word are used to signal the address and the

8

voltage levels provided at different terminals of a further staticisor unit, the F-Staticisor unit FST (FIG. 1b) which, in similar manner to the L-Staticisor LST, above referred to, is itself controlled by portions of a dynamic pulse form signal fed thereto.

A change-over or Staticisor Switch (FIG. 1a)

$\frac{SS}{2}$

function is to translate a dynamic pulse form signal into suitable static control voltages for the unit YSG whereby the latter provides a deflection of the tube beam in the Main Store MS to a raster line whose address is that indicated by the pulse signal fed to the staticisor unit.

The machine shown is capable of performing one simple type of arithmetical operation only, namely subtraction and this is effected in the arithmetical organ or Actual suitable static control voltages for the unit YSG whereby the latter provides a deflection of the tube beam in the when the machine from automatic to manual operation while a series of switches, normally closed when the machine is in the automatic running condition, permit the setting of the L-Staticisor LST and the F-Staticisor FST in any desired one of their various conditions without the need of a special input pulse signal the various conditions. The machine from automatic to manual operation while a series of switches, normally closed when the machine is in the automatic running condition, permit the setting of the L-Staticisor LST and the F-Staticisor FST in any desired one of their various conditions without the need of a special input pulse signal for the static permit the setting of the L-Staticisor LST and the F-Staticisor FST in any desired one of their various conditions without the need of a special input pulse signal for the static permit the setting of the L-Staticisor LST and the F-Staticisor FST in any desired one of their various conditions.

KLC 2

and a key (FIG. 1b) KSC permit correction of any entry under manual control conditions or clearance of the Main Store.

A number of further waveform generators governing the operation of the machine including an X-scan generator XWG (FIG. 1b) by which the beams of all the cathode ray tubes used are caused to scan in the X-direction in unison during each beat interval, subject to their being brightened to operative level. These waveforms and their generators will be referred to and described later in the more detailed description of the various parts. In broad outline the operation of the machine is as follows:

The initial setting up of the various number and instruction words in the Main Store MS is effected manually. To accomplish this the Staticisor Switch (FIG. 1b)

SS

is thrown to the manual position (i.e. opposite to that shown) and the appropriate Y level of the cathode ray tube in the Main Store MS at which recording is desired is then selected by closure of the appropriate one or combination of Switches S0-S4 associated with the L-Staticisor unit LST. Operation of any one of the keys K0-K39 (FIG. 1a) of the typewriter TPR serves to record a dash symbol at the appropriate position along the length of the particular raster line occurring at the chosen Y level. By repeated selection of different Y-levels by means of switches S0-S4 and operation of the appropriate typewriter keys any desired number of the various lines of the Main Store may be filled with the requisite mathematical numbers and the related instruction words for the desired computation.

Number words related to the mathematical quantities being dealt with will consist of an appropriate collection of binary digits up to the maximum capacity of one line of the tube which, in this case, is forty digits.

The instruction words will in general comprise two separate sections, the first consisting of a group of binary digits, which are related to and serve to signal the particular address, i.e. the particular line or Y-level in the Main Store MS at which a desired number word is located and a second section, again composed of a collection of binary digits which serve to signal and control the nature of the function which is required to be carried out on the particular number chosen by the previous address section of the word. In general with a machine of the simplest type described a total of five binary digit symbols will suffice to select any desired address level while a total of three binary digit symbols is sufficient to set up any of the different function operations which can be carried out. Accordingly the 1st, 2nd, 3rd, 4th and 5th digits of the word are used to signal the address and the

14th, 15th and 16th digits to signal the functional opera-

If erasure is desired at any time during this manual setting-up operation it can be effected by throwing keys

## KLC

and KSC. Regeneration of the information recorded in the Main Store is effected during each alternate (scan) beat and therefore starts immediately after insertion of any digit so that the numbers or words put into the store are available for use or alteration indefinitely thereafter.

Assuming all the required number and address words have been inserted in the Main Store MS then the normal automatic operation cycle can be initiated. This is effected by throwing the Staticisor Switch

to its autoposition (as shown) whereupon continuous operation on the basis of four beats to every bar will commence. Each beat will be initiated by a prepulse from the Prepulse Unit PPU. During such automatic operation in the first (Scan 1) beat regeneration takes place 25 tion from the F-Staticisor. in all storage units and while it is doing so in the control unit CL a control instruction number (n) already stored in control unit CL on one, the CI line, of its two levels will be increased by 1 automatically by a pulse sent out from the test unit TU and the resultant new num- 30 tinuous automatic cycle. For this purpose the switch ber (n+1) simultaneously read out of the control unit CL through the opened Instruction Gate IG to the L-Staticisor LST where the 1st and 5th digits of the number will set such L-Staticisor to a condition which provides a series of static output voltages for controlling the Y- 35 shift generator YSG during the next following (action) beat such as will adjust the Y-level of the Main Store MS during that action beat to that of the next instruction number which is to be read out from the Main Store MS.

On the next (Action 1) beat there is no regeneration 40 anywhere but the newly selected or present instruction number is read out from the Main Store MS through the opened Outward Transfer Gate OTG into the store CL at the alternative or P.I. level of the latter. The beam scanning level of the storage tube of this unit is suitably 45 altered by a waveform supplied from the unit GYWG.

In the next following (Scan 2) beat, the new, present instruction word in the store CL is read out through the Instruction Gate IG to the F-Staticisor FST and the L-Staticisor LST. The F-Staticisor is operated by the 50 14th-16th digits of such words to provide a series of different voltages which when applied to the various circuit elements such as the Inward and Outward Transfer Gates ITG and OTG, the erase, writing, adding, subtracting or reading circuits of the various store units serve to set up 55 the necessary routing and control arrangements for the particular function operation next to be performed. The address digits, i.e. the 1st to 5th digits of the same word cause similar operation in the L-Staticisor LST to reset the Y-shift generator YSG for the Main Store MS to the 60 particular new level of the number stored in the Main Store MS which is next required to take part in the chosen operation.

In the fourth (Action 2) beat the aforesaid present instruction is obeyed by the transference of the selected 65 number out of the main store MS over the particular path and through the operation of the appropriate other units as selected by the F-Staticisor FST to a destination which will normally be the Accumulator A.

In the next following operation the control instruction 70 (n+1) previously existing at the first (C.I.) level in the unit CL is again increased by 1 whereupon the cycle is repeated substantially along the lines described. By arranging that the successive present instruction words read out from the Main Store define the required programme 75 sisting of positive going square pulses during the period of

10

of operation, the required computation will be completed automatically.

If, at a certain point in the programme of operation, the next step is conditional upon the result of the partial solution at that point, then the present instruction brought into use from the Main Store is arranged to cause a testing operation by the unit TU which, according to the result obtained, either causes continuance with one sequence of instruction words by again providing the addition of 1 to the control instruction in control unit CL or, alternatively, by providing the addition of 2 to such number causes diversion to a fresh series of present instruction words. The completion of the programme or the suspension of operation at any time is arranged to cause operation of the Stop Unit SU which suspends the operation of the Prepulse Unit PPU and illuminates the Stop Lamp SL.

In the particular machine described the Accumulator or arithmetic unit A is adapted when required to cause 20 subtraction of a given number written in from that already stored in the accumulator tube but of course a variety of other arrangements such as for effecting addition or multiplication may be used instead or even provided at the same time and selected by appropriate gating opera-

In addition to the manual insertion of information into the store it may be necessary, either for initial setting up purposes or for subsequent test purposes, to operate the machine one bar at a time instead of according to a con-

> SS 2

is held in the manual position and the appropriate function set by operation of one or more of the switches S13 to S15 associated with the F-Staticisor. The operation of the machine is then initiated for one bar only by operation of key KSP.

The various units and their manner of operation will now be described in greater detail. The basic timing of the machine shown in FIGS. 1a and 1b is controlled by a clock pulse generator circuit CPG (FIG. 1b) which provides a series of square pulses whose period time is 8.5 microseconds. These pulses shown in diagram (i) of FIG. 2 will hereinafter be called Clock pulses. The time period of a total of 45 of these Clock pulses is assigned to each beat of the machine and of this period the time required by 5 Clock pulses is assigned to the requisite flyback motion of the beam of each cathode ray tube storage device before each linear scanning motion leaving a total of 40 Clock periods for the actual composition of each number or word. The dynamic form signal for each digit of a number or word is arranged to fall within the period of 1 Clock pulse and the machine therefore has a capacity, as already stated, of 40 digits in each number or word.

The Clock pulses are applied to a divider circuit DV1 (FIG. 1b) which can be of any suitable form to provide an output pulse for every five input pulses as shown in waveform (ii) of FIG. 2. These pulses will hereinafter be called DIV1 pulses and are then applied to a further divider circuit DV2 which again is of any suitable form to provide an output pulse for every nine input pulses as shown in waveform (iii) of FIG. 2. These pulses, which occur one in synchronism with each 45th Clock pulse will hereinafter be referred to as the DIV2 pulses.

The pulses from divider circuit DV1 are applied as one triggering input to a flip-flop circuit BOPG, the other triggering input of which is supplied from the divider circuit DV2 by way of a gate circuit G1 which is opened by the further supply thereto of the pulses from the divider circuit DV1. The consequential output from circuit BOPG is a waveform as shown in diagram (iv) of FIG. 2, con11

Clock pulses 1 to 5 and then a quiescent period until the end of Clock pulse 45 and so on. This waveform which is used to ensure suppression of all the cathode ray tube beams during the flyback time following each line scan, will hereinafter be called the Black-Out waveform.

The requisite repetitive saw-tooth waveforms for causing linear scanning movement of the various cathode ray tube beams in the X direction are provided by the X-time base generator XWG (FIG. 1b) which is controlled by the Black-Out waveform so that the flyback portion com- 10 mences at the instant of commencement of each positive going Black-Out pulse and the linear scanning portion at the instant of termination of each Black-Out pulse. One of the two (push-pull) X-time base waveforms, hereinafter called the XTB waveform is shown in diagram 15 (xiii) of FIG. 3. The time scale of this diagram together with that of the redrawn Black-Out waveform (iv) has been reduced by 4 as compared with FIG. 2 to illustrate the 4 complete beats of a single bar S1, A1, S2 and A2.

As explained in detail in the aforesaid paper by F. C. 20 Williams and T. Kilburn the setting up of one or the other of the two different forms of discrete charge upon the cathode ray tube screens, representative respectively of the binary digits "0" and "1" is effected by intensity modulation of the tube beam for time periods of different 25 lengths whereby, due to the concurrent X scanning movement of the beam, a "dot" or a "dash" charge pattern is provided. For effecting such beam modulation the machine is provided with a dot pulse generator DTPG (FIG. 1b) and a dash pulse generator DSPG each of which are 30 supplied with the Clock waveform to initiate triggering of suitable pulse generating circuits, the constants of the circuit of DTPG being such as to provide a series of two microsecond negative going pulses each coincident with a Clock pulse as shown in diagram (v) of FIG. 2 and the 35 corresponding constants of the circuit of DSPG being such as to provide a series of five microsecond pulses each coincident with a Clock pulse as shown in diagram (vi) of FIG. 2. By supplying the output from each of the circuits DPTG and DSPG through gate circuits G2 and 40 G3 which are controlled by an output from the Black-Out waveform generator BOPG the Dot and Dash pulses are inhibited during the time of the first five Clock pulses of each complete beat of 45 pulses so as to provide a series of separate groups of Dot and Dash pulses, 40 in number, 45 and each coincident in time respectively with Clock pulses 6 to 45. These Dot and Dash waveforms are conveniently made available through buffer amplifiers BA1, BA2.

In order to allow selection of specific ones of said Dot or Dash pulse series and for other similar purposes there 50 are provided a group of 40 single pulse waveforms, each on separate leads and each consists of a single 5 microsecond pulse coincident in timing with one or other of the Dash pulses. These waveforms will hereinafter be referred to as the "p pulses" and diagram (viii), FIG. 2, 55 shows the first of the group comprising a negative-going pulse synchronised in time with the first Dash pulse and called, for convenience in computing, the "p0" pulse since it coincides with the position in the group of 40 pulses, of the lowest significant figure 20 in the binary scale (for convenience, the order of significance of the digit positions is assumed to increase from left to right). The next pulse of the group, the "p1" pulse (denoting 21 in the binary scale) is shown in diagram (ix), FIG. 2, and is coincident in time with the second Dash pulse while diagrams (x) and (xi) respectively illustrate the next or "p2" pulse  $(2^2)$  and the last or "p39" pulse  $(2^{39})$ . The intervening pulses of the group are not shown since their form will be obvious. These "p" pulses are conveniently produced, in the manner described in detail later with ref- 70 erence to FIGS. 20 and 21 by a series of trigger circuits PPG (FIG. 1b) all of which are supplied with the Dash waveform. Normally each circuit is in inoperative condition and produces no output but each can be condi-

sient voltage in readiness to provide an output pulse coincident with the arrival thereat of the next Dash pulse. The first trigger circuit  $p^0$  of the series is conditioned by the application thereto of the Black-Out waveform while the subsequent trigger circuits p1 to p39 are each conditioned by voltages derived from the immediately preceding circuit. The last circuit  $p^{39}$  is reset by the leading edge of the next following Black-Out pulse from the circuit BOPG. For convenience in illustration the various output leads from the p pulse generator are shown collectively as a single multiple conductor and the significance of any particular single conductor from such multiple is indicated by the addition of the particular p-pulse number involved thereagainst at its point of attachment to any

12

As described in detail in the aforesaid paper by F. C. Williams and T. Kilburn the reading or interpretation of an already stored charge pattern on a cathode ray tube screen is effected by sampling a portion only of each discrete charge as the cathode ray tube beam is sweeping thereacross and for the purpose of controlling such sampling or reading instants a further series of pulses, hereinafter called the Strobe pulses are provided. pulses which are shown in diagram (vii), FIG. 2, are positive-going and have about one microsecond duration commencing at instants slightly later than the leading edges of the Dot and Dash pulses. They are derived in the circuit shown from a pulse generator circuit SPG (FIG. 1b) triggered from the Clock pulse waveform and fed, in similar manner to the Dot and Dash pulses, through a gate circuit G4, controlled by the Black-Out pulses, to a buffer amplifier BA3.

As already referred to, the natural decay of the cathode ray tube charge patterns with time, owing to leakage necessitates their frequent and repeated regeneration and this is effected where necessary in the machine described by assigning alternate X-time base scans to regeneration and using the intervening scans for operational purposes. These periods are those known as the scan and action beats respectively, each four beat bar therefore comprising a Scan 1 beat, an Action 1 beat, a Scan 2 beat and an Action 2 beat. For the purpose of effecting control of various elements during these alternate beats, two further square waveforms, at half the frequency of the Black-Out and XTB waveforms are provided as shown in diagrams (xiv) and (xv) of FIG. 3. They are derived from square wave generator circuit HWG (FIG. 1b) comprising a flip-flop circuit triggered from one state to the other by the Black-Out waveform. One output comprising positive-going half cycles coincident with the scan beat periods will hereinafter be referred to as the Halver-S waveform while a second paraphase output having its positive-going half cycles coincident with the action beat periods will hereinafter be referred to as the Halver-A waveform.

The necessary transverse or Y deflection of the cathode ray tube beam of the Main Store MS is effected by a stepped waveform as shown in diagram (xvi) of FIG. 5 which is still further reduced in its time scale as compared with FIGS. 2, 3 and 4 to show a complete Y scan cycle occupying the time period of some 32 lines in the complete raster corresponding to a storage capacity of 32 separate words or numbers. The Halver-S waveform to which this Y-Shift waveform is time related has been redrawn to the same time scale in diagram (xiv), FIG. 5. As will be seen the Y-Shift waveform comprises a series of separate square pulses of progressively changing amplitude with the intervening and equal time periods at a, normally, common voltage level. The aforesaid differing pulses coincide in timing with the scan beat periods of the Halver-S wave and consequently provide for the progressive shift of the tube beam in the Y or transverse direction whereby regeneration of each stored word or number is effected regularly and in turn by the X-Scan tioned for operation by the application of a positive tran- 75 movement which takes place during each of these scan

13

beat periods. The intervening voltage level periods coincide in time with the action beat periods of the Halver-S wave and, as described in the aforesaid paper by F. C. Williams and T. Kilburn and as referred to later, the voltage level of any one of these intervening periods can be set to any one of the 32 levels marked by the aforesaid differing or scan period pulses for the purpose of selecting any one of the storage lines of the charge pattern raster during an action period. Examples of such change of voltage level of the intervening periods is indicated in 10 dotted lines in diagram (xxxv), FIG. 5.

The above described Y-Shift generator circuit YSG (FIG. 1b) resembles that described in detail in FIG. 35 of the aforesaid paper by F. C. Williams and T. Kilburn and comprises a cascade of scale-of-two-counter circuits 15 C0, C1, C2, C3 and C4 supplied at the first counter circuit C0 with the Halver-S waveform. Each counter produces square waves which are successively submultiples of the Halver-S wave frequency. The output of each counter circuit is added to the Halver waveform and is then 20 applied as one of two alternative controlling inputs to an associated switching valve SV0, SV1, SV2, SV3 and SV4 and the respective outputs from each of the latter valves, when combined in suitable proportions serve to provide a controlling potential for a Y-Shift valve YSV which by its 25 two opposite phase outputs provides the requisite pushpull Y-Shift waveforms for the cathode ray tube or tubes of the main store. The alternative controlling inputs for the switching valves SV0 to SV4 is provided by the L-Staticisor circuit LST already referred to and which 30 This circuit serves to will be described in detail later. select under the control of the 1st to 5th digits of an instruction word signalled to the L-Staticisor, such combination of switching valves SV0 to SV4 for their operation during an action beat period of the Y-Shift waveform 35 as will set such Y-Shift in the cathode ray tube of the Main Store at the required level to deal with the chosen line of the raster containing the required number or instruction word. In spite of this change during any action beat, the next following scan beat automatically continues 40 regeneration of the raster line immediately following that which was regenerated in the previous scan beat so that although the raster line circuit during successive action beats may shift from one to the other of any of the 32 lines of the store tube, regeneration takes place during intervening scan beat periods smoothly and regularly.

A number of other waveforms are involved in the machine but the form and production of these will be dealt with at the time of description of the unit with which they are concerned.

The Main Store MS (FIG. 1b) closely resembles in general form that described in the aforesaid paper by F. C. Williams and T. Kilburn and will be described in greater detail later with reference to FIG. 22. Broadly it comprises the cathode ray tube 10 with pick-up plate 11 and a regenerative loop comprising an amplifier 12, reading unit 13 and writing unit 14 whose output is connected to the modulation grid of the tube. The X-deflector plates are supplied from the X-time base generator XWG while the Y-deflector plates are supplied from the Y-Shift generator YSG. For the purpose of sampling only the first portion of each stored charge, whether it be a dot or a dash, the read unit 13 is supplied with the Strobe waveform as described in said paper by F. C. Williams and T. Kilburn. During regeneration of this storage tube in each scan beat a series of dot signals are continuously written into the tube by the write unit 14 under the control of the Dot waveform applied thereto and a dot is accordingly always provided at each digit position unless the presence of a dash signal exists in the 70 input to the write unit whereupon a fresh dash signal, derived from the Dash waveform also supplied to the write unit, is made to extend the dot pulse to cause recording of a dash. Such dash signal input to the write unit can be derived either from an external in- 75 additional adding unit 30 to which an external writing

14

put from the Inward Transfer Gate ITG or from the signal plate 11 by way of the regenerative loop of amplifier 12 and read unit 13. By such arrangement it is clearly possible to erase any existing dash pulse signal in the storage tube by the simple process of breaking the regenerative loop during the period of such signal whereupon a det is automatically written in its place. This erasure can be effected by applying over lead 15 a suitable waveform for inhibiting or blocking the operation of the read unit 13 at the appropriate time instants. The output signal from the pick-up plate 11, as existing in the storage tube 10 at any particular instant, can be read out from the unit 13 and made available to the rest of the machine through the Outward Transfer Gate OTG.

The arithmetical organ or Accumulator A (FIG. 1a) comprises a storage device of the kind described in the aforesaid paper by F. C. Williams and T. Kilburn and also dealt with later in connection with FIG. 22. It includes a cathode ray tube 16 with pick-up plate 17, amplifier 18, read unit 19 and write unit 20 whose output is connected to the modulation grid of the cathode ray tube. This particular tube, being concerned with only single line storage is not provided with any form of Y-Shift but is, of course, applied with the XTB waveform from the X-time base generator circuit XWG. The write unit 20 is supplied with both Dot and Dash waveforms for operation in the manner as already described in connection with the main store and the read unit 19 is similarly supplied with the Strobe pulse waveform for the requisite sampling control. This Accumulator A, however, is provided with an additional arithmetical element comprising a subtracting unit 21 located between the read unit 19 and write unit 20 and external writing input to the Accumulator A is fed as a second input to this subtracting circuit. The operation of this circuit is such that the additional write input to the subtracting unit 21 may be subtracted from the number content already in the Accumulator and the result rewritten into the storage tube 16 and provided simultaneously as an external read output if required. Alternatively, it may be arranged that, by applying an appropriate erasing wave to the read unit 19, e.g. to the suppressor grid of a gate valve, such as that of valve V110, FIG. 22, which selects the transient signals from the amplifier 18, so as to break the regenerative loop, then the external write input to the subtracting unit 21 will in effect, be subtracted from zero since there is no stored number present within the tube 16 and the result will be a number which is minus the number represented by the original write input to the subtractor unit 21. This minus number or complement is written into the tube 16 of Accumulator A. Such subtracting arrangements are already very well known in the computer art and have been described and discussed in the literature such as, for example, the various "Progress Reports" upon the EDVAC machine made by the Moore School of Electrical Engineering, University of Pennsylvania.

The required inhibition of the reading unit 19 is effected by the application, when required, of suitable potentials to a controlling gate circuit. The provision of these potentials necessary to alter the normal subtracting operation of the Accumulator unit A from one which deals with the existing word or number already in store to one which subtracts from zero to provide a complement, is effected by the F-Staticisor FST which will be described later.

The control unit CL (FIG. 1a) is effectively a combination of a control register and a current instruction store and comprises a single cathode ray storage tube 25 provided with a pick-up plate 26 and a regenerative loop consisting of amplifier 27, read unit 28, write unit 29 feeding the modulation grid of the tube 25 with its output. tube has its X-deflector plates supplied from the X-time base generator XWG and has its Y-deflector plates supplied from the unit GYWG. In this circuit is included an

input may be fed and, for an action analogous to that of the subtraction within the Accumulator A, such external writing input may either be added arithmetically to the number already existing within the store, or, alternatively, by applying a suitable erasing control to the read unit 28, may be written into the storage tube 25 in place of the number already existing on the particular line of the two lines available which is being scanned. The form and organisation of adding circuits are already very well known in the computer art and have been 10 widely discussed in the literature, see for example, the various "Progress Reports" upon the EDVAC machine made by the Moore School of Electrical Engineering, University of Pennsylvania, Proc. I.R.E., December 1948, pages 1452-60; "A Digital Computer for Scientific Ap- 15 plications," by West and Deturk; and U.S.A. patent specification No. 2,429,227, filed June 11, 1945, by P. J. Herbst.

The F-Staticisor (FIG. 1b) comprises a plurality, in the present case three, identical sections one for each of the function-determining digits of the instruction word which 20 is to be staticised thereby. FIG. 6 shows the circuit arrangement of one staticisor section n corresponding to the (n+1)th digit of the word. This element comprises a two-state trigger circuit of valves V1, V2 provided with anode-to-suppressor-grid cross coupling. The quiescent 25 condition of the trigger circuit is that in which V1 is conducting to its anode and this state is maintained or the element is reset to it at the commencing of every scan beat by negative pulses derived by differentiation of the Halver-A waveform which are supplied to the control grid 30 of valve V2 by way of terminal 31. The positive-going differentiated pulses which occur at the commencement of each action beat period of the Halver-A waveform are ineffective owing to the positive bias supply for the control grid of valve V2.

A gate circuit of the multiple diode type controls the triggering input to valve V1 and comprises diodes D1 and D2 with a common cathode resistor R1 returned to a source of negative potential and whose anodes are returned respectively to positive potential sources by way of resistors R2, R3. The anode of diode D2 has applied thereto by way of terminal 32 the particular p-pulse waveform applicable to the digit concerned, i.e. either the p13, the p14 or the p15 waveform in the present machine while the dynamic instruction word or other input controlling voltage is applied to the anode of the other diode D1 through terminal 33. This latter voltage is supplied through the related manual setting switch S13, S14 or S15 shown in FIG. 1b. Both input voltage pulses the potential of the control grid of valve V1 unless they occur simultaneously for the reason that only when both diodes are cut off will the common cathode point move negatively. When this occurs, i.e. when a Dash pulse exists in the dynamic instruction word coincidental with 55 when the Staticisor Switch the particular digit position of the staticisor section concerned, valve V1 is cut off at its suppressor grid and the circuit is triggered.

Four alternative outputs are made available from this staticisor element to provide controlling voltage levels which, by appropriate selection, can have desired values for application to the various gate and other circuits throughout the machine which determine the path of transfer of any signal and also the particular form of operation which is performed by the machine during any 65 one bar of operation. These four alternative outputs are derived across the cathode load resistances of cathode follower valves V3, V4, V5 and V6. Valve V3 derives its controlling input from the suppressor grid of valve V2 while valve V4 similarly derives its controlling input from 70 the suppressor grid of valve V1 so that in the quiescent ("0") condition of the staticisor element when valve V1 is conducting to its anode the potential at the output terminal 0/n (sup) of valve V3 is -60 volts whereas the potential at the corresponding terminal 1/n (sup) of valve 75 7. The portion of this circuit which generates the Y-Shift

16

V4 is 0 volts. The diodes D3 and D4 are provided to fix the zero voltage levels obtained at these output termi-When the staticisor element is triggered to the opposite or "1" condition by the input of a dash or equivalent potential to the anode of diode D1 in coincidence with the occurrence of a suitable negative voltage, e.g. the particular p pulse for the element at the anode of diode D2, then the potential distributions are reversed and the 1/n (sup) terminal falls to -60 volts and the 0/n (sup) terminal rises to zero volts. The other output terminals 0/n and 1/n are similarly fed through the cathode follower valves V5 and V6 from tapping points on potential divider networks of resistors R6, R7 and R8, R9 connected between a source of negative potential and the anodes of valves V1 and V2 respectively. Diodes D5, D7 with their cathodes connected to a source of positive potential (+118 volts) and diodes D6, D8 with their anodes returned to a source of negative potential (-14 volts) limit the excursions of the grids of valves V5 and V6 with the result that in the quiescent or "0" condition of the staticisor element the 0/n terminal is at -10 volts and the 1/n terminal at +120 volts. These conditions are similarly reversed when the element is triggered to the "1" condition.

The L-Staticisor LST (FIG. 1b) comprises a plurality of sections in similar manner to the F-Staticisor and the circuit arrangement of each section is substantially identical with that of FIGURE 6 except that the four output cathode follower valves V3, V4, V5 and V6 with their associated diode circuits shown below the dotted line are omitted and a single output is taken from the suppressor grid of valve V2 to the associated switching valve of the Y-Shift generator YSG. Such output from each staticisor section is taken to the switching valve of the Y-scan generator by way of a gate circuit, G5 . . . G9, FIG. 1b, which is itself controlled by the Halver-A waveform so as to be open only during action beats. In this way the staticisor can be set up during a scan beat while the normal sequential scanning raster is being provided by the Y-scan generator and then rendered instantly effective upon the latter at the beginning of the following action There are five such elements in the L-Staticisor with the respective inputs to the anodes of their diodes D2 comprised of the p0, the p1, the p2, the p3 and the p445 p-pulse waveforms so as to select the chosen address defining digits of the dynamic instruction word. The inputs to their respective diodes D1 are supplied in common with those of the F-Staticisor from the Staticisor Switch SS through manual switches S0 to S4 like the are negative-going but neither will be effective to depress 50 F-Staticisor, the presence of "1" dashes at any digit position can be simulated in the manual operation condition by the closure of the appropriate one of said manual switches.

The switches S0-S4 and S13-S15 are provided so that

SS

is in the manual position and the instruction word nor-60 mally supplied from the control unit CL is replaced by the Halver-A wave the presence of "1" digits is simulated in all elements wherever the manual switch happens to be closed so that opening of any manual switch simulates the presence of an "0" at the corresponding digit position with the consequent facility of setting up either staticisor manually in any one of its various states so as to provide any one of the corresponding function or address selecting controls.

The unit GYWG (FIG. 1a) which provides the necessary waveform to control the Instruction Gate IG and also the waveform to shift the beam of the storage tube 25 of the control unit CL between one or the other of its two alternative scanning levels to deal respectively with the CI and PI words is shown in schematic form in FIG.

waveform for the cathode ray tube 25 comprises two cascade connected trigger circuits 35 and 36 each comprising flip-flop type arrangement triggered in one direction by one input and reset by a second separate input. trigger circuit 35 is set by each prepulse, i.e. the pulse signal which initiates the operation bar of the machine and shown in diagram (xvii) of FIG. 4 which is again further reduced in its horizontal time scale as compared with FIG. 3 in order to show several complete bar periods. The circuit 35 is reset by negative-going pulses shown in 10 diagram (xix) of FIG. 4 obtained by differentiating the Halver-S which is also redrawn in FIG. 4 in diagram (xviii). The trigger circuit 35 provides two output waveforms which are respectively positive and negative-going during the S1 beat immediately following a prepulse. 15 These waves are indicated at diagrams (xx) and (xxvi) of FIG. 4 and are hereinafter referred to as the S1 and the Para-S1 waveforms. The S1 waveform is differentiated and the negative-going pulse selected as shown in diagram (xxi) of FIG. 4. This pulse is then used as a 20 triggering input to the second trigger circuit 36 which is again reset by differentiated Halver-S waveform of diagram (xix). This resetting action is arranged to occur at the end of Scan 2 beat by making the differentiation of the S1 waveform with a slower time constant. resultant waveform provided from one side of the trigger circuit is as indicated in diagram (xxii) of FIG. 4 and will hereinafter be referred to as the CL Y-Plate waveform.

A waveform as indicated in diagram (xxix) of FIG. 4 30 and hereinafter referred to as the Instruction Gate waveform is produced in a gate circuit 37 by feeding thereto the Halver-A wave redrawn in diagram (xxv) of FIG. 4 and the combination of the paraphased S1 waveform, diagram (xxvi) from the trigger circuit 35 and the inverse form of the CL Y-Plate waveform available at the output point 38 of trigger circuit 36 and shown in diagram (xxvii) FIG. 4. The combined wave fed to the input point 39 of the gate 37 will be of the form indicated in diagram (xxviii) of FIG. 4 so that the output 40 wave from this gate, conditioned by the Halver-A waveform will be as indicated in diagram (xxix) of FIG. 4, falling from the quiescent level of zero to -60 volts during the S1 and S2 beat periods. This waveform is used for application to the Instruction Gate IG so as to open 45 the latter during such scan beats.

FIG. 7 also includes the action waveform generator AWG used to provide waveforms, hereinafter referred to as the Action waveform and the Para-Action waveform for cutting off the beam current in the cathode ray tubes of the Accumulator A and control CL and also for conditioning the Outward Transfer Gate OTG of the Main Store MS.

Referring still to FIG. 7 the control Y-Plate waveform available from the flip-flop circuit 36 is differentiated and the resultant negative-going pulses corresponding to the negative-going edges of the wave of diagram (xxii) of FIG. 4 are fed to form one triggering input of a third flip-flop circuit 40 while the inverted form of this wave derived from the opposite side of the circuit 36 is similarly differentiated and the resultant negative-going pulses selected and fed by way of the Staticisor Switch

## SS

also to the same triggering input of the circuit 40. When the Staticisor Switch is closed, i.e. in its auto-position there will, as shown in diagram (xxiii) of FIG. 4, be negative pulses coincident with the commencements of both the Action 1 and Action 2 beats whereas when such switch is open in its manual condition there will be a negative pulse only at the commencement of the Action 2 beat. The other triggering input to the circuit 40 comprises a differentiated version of the Halver-A waveform which is illustrated in diagram (xxv) of FIG. 4 and acts 75

to reset such trigger circuit by its negative-going pulses. The resultant Action waveform output from the circuit 40 is shown in diagram (xxx) of FIG. 4 for the automatic operating condition and in diagram (xxxi) for the manual operating condition. The inverse or para-phased Action waveform also available from the opposite side of the circuit 40 is illustrated in diagram (xxxii) for the auto-condition. In the manual operating condition the first or Action 1 beat portion is absent as shown in dotted The inhibition of this portion of the Action and Para-Action waveforms during the Scan 1 beat is necessary so that instructions set up manually in the staticisors may be utilised and be obeyed once only by causing the machine to perform a single operation. If this provision were not made any instruction word set up manually on the staticisors would be effective twice within a single bar. It will also be observed that the presence of any Action or Para-Action wave portions is dependent upon there being a prepulse at the beginning of the bar.

The Action waveform is fed to the writing units of the Accumulator and control regenerative loops which are so arranged that their respective cathode ray tubes are normally bright, i.e. operative, during all beats both scan and action except those Action 1 and Action 2 beats in which the Action wave departs from its quiescent level. The Action waveform is not however applied directly to the brightness control of the cathode ray tubes but is applied in each case through a multiple diode gate or similar circuit which is controlled by potentials developed in the F-Staticisor as a result of the setting of the latter in consequence of the particular value of the instruction word digits allotted thereto. Thus by arranging that the Action wave fed to the Accumulator A is inhibited when the F digits 14 and 15 are "1" and that the Action wave fed to the control CL is inhibited when the same digits are both "0," certain required dark and bright conditions of the Accumulator and control cathode ray tubes during beats Action 1 and Action 2 may be realised as referred to in detail later.

The Para-Action waveform fed to the Outward Transfer Gate OTG ensures that the gate is closed at all times except when the Action waveform departs from the quiescent level during Action 1 or Action 2 beats. In order to comply with the requirements of certain instruction digit combinations the outward transfer gate circuit is also arranged to be capable of being inhibited by the staticised F digits 14 and 15 of an instruction word whenever the latter are both "1", the Outward Transfer Gate OTG thus being opened only upon coincidence of the paraphased Action waveform and the staticised "0" digits in positions 14 and 15.

Reference will now be made to FIG. 8 of the drawings which shows the circuit arrangements of the Stop and of the Prepulse Units of FIG. 1a. For the purpose of initial explanation of the stop circuit which is shown at the bottom part of FIG. 8, the prepulse circuit comprising valves V10 to V13 and the associated diodes D11 to D15 will be considered as a device which will continue to generate pulses, one at the commencement of each four beat interval so long as the controlling input terminal 42 of the prepulse switch PS is maintained at or above earth potential. During normal automatic operation with the prepulse switch in the on or closed position the cathode of the cathode follower valve V9 of the stop circuit is maintained at a positive potential so that a continuous train of prepulses is produced.

The Stop Unit itself consists of a trigger circuit arrangement of valves V7 and V8 and associated diodes D9 and D10 which is normally maintained in the condition in which valve V7 is conducting by the negative prepulses derived from valve V13 of the prepulse unit later to be described. These negative-going prepulses are applied to the grid of valve V8 at the instants of the beginning of each Scan 1 beat. The control grid of valve V7 is returned through suitable leak resistors R11, R12,

R13 to output points of the F-Staticisor so selected that when the particular F digit combination appropriate to the signal to stop (actually 1, 1, 1 at the 13th, 14th and 15th digit positions as explained later) is set up during a Scan 2 beat the trigger circuit of valves V7 and V8 is caused to reverse so that valve V8 conducts and the potential at the cathode of valve V9 falls below earth, thereby inhibiting the operation of the Prepulse Unit. The succeeding prepulse which would normally ensure that the stop circuit was retriggered to the condition where 10 valve V8 is again cut off is thus not available and the stop circuit remains in this stop condition indefinitely until a single prepulse is caused to issue manually by operation of the key KSP and thus causing the circuit to be re-The Stop Lamp SU is associated with the 15 triggered. anode circuit of valve V8 as indicated so that when the stop instruction is obeyed and valve V8 is conducting, the lamp is illuminated.

The circuit of the Prepulse Unit has to perform the the prepulse switch PS is in the on or closed position and, whenever the switch is in the off or open position, of releasing a single prepulse only whenever the key KSP is operated. The waveforms related to the understanding of this prepulse circuit are shown in FIG. 4. The 25 Halver-A wave, FIG. 4 diagram (xxv), which is negative-going during scan beats is differentiated to produce the negative-going pulse wave of diagram (xxxiii), FIG. 4, at the anode of diode D15. The positive pulses resulting from the differentiation are removed by the conduc- 30 tion of diodes D13 and D15. Any one of these negative pulses at the anode of diode D15 could be employed as a prepulse since they are of the correct timing, occurring at the beginning of every scan beat. They are however normally prevented from reaching the output terminal 43 35 which is fed by way of the cathode follower valve V13, by reason of the fact that the diode D15 forms a part of a diode gate circuit including diodes D12 and D13 and that diode D12 is held conducting by the standing potential of the suppressor grid of valve V11.

Valves V11 and V12 and their associated diodes D11, D12 and D13 form a trigger circuit which is normally held in the condition in which valve V11 is conducting by the application to the control grid of valve V12 of the negative pulses, shown in diagram (xxxvi) of FIG. 4, obtained by the differentiation of the Counter 0 waveform illustrated in FIG. 4 (xxxiv) and derived from that portion of the Y-Shift generator YSG. The positive pulses of the differentiated wave are ineffective since the grid of valve V12 is already at zero potential. The valve V10 which is conducting to its screen when the prepulse switch PS is in the closed or ON position, has the differentiated Counter 0 waveform of diagram (xxxiv), FIG. 4, applied to its suppressor grid but only the positive pulses are effective owing to the negative bias applied to the suppressor grid. The anode waveform of valve V10 in this condition is shown in diagram (xxxvii) of FIG. 4 and these negative pulses, which are fed to the control grid of valve V11 produce triggering of the circuit of valves V11, V12 at the commencement of alternate Action beats so that the waveform at the suppressor grid of valve V11 is that shown in diagram (xxxviii) of FIG. 4, the circuit being retriggered by the negative pulses of the differentiated Counter 0 waveform as previously explained. The negative-going square wave at the sup- 65 pressor grid of valve V11 effectively forms a gating waveform which operates to open the diode gate of D12 and D15 so that the differentiated Halver-A waveform pulses which occur within the gate intervals are passed by way of the cathode follower valve V13 to the output terminal 70 43 as prepulses.

When the prepulse switch PS is in the OFF or open position the valve V10 and the diode D14 and the resistors R14, R15 and the capacitor C1 form a single pulse circuit which permits the circuit of valves V11 and V12 to be 75

triggered once only for each operation of the single prepulse key KSP irrespective of any bounce in the contacts of that key. It will be appreciated that as the time intervals between successive pulses of the waveform of diagram (xxxiii) of FIG. 4 is of the order of 0.5 millisecond bounce of the contacts of key KSP, simulating repeated operation might cause several prepulses to be released. The negative bias potential provided by way of resistor R15 serves to maintain the valve V10 cut off while the potential at the anode of diode D14 is held just above earth, the diode conducting by virtue of the connection of its anode through the normally closed contact of key KSP and resistor R14 to a positive potential source and its cathode being held approximately 5 volts positive by the connection thereof to the cathode of the output cathode follower valve V13.

20